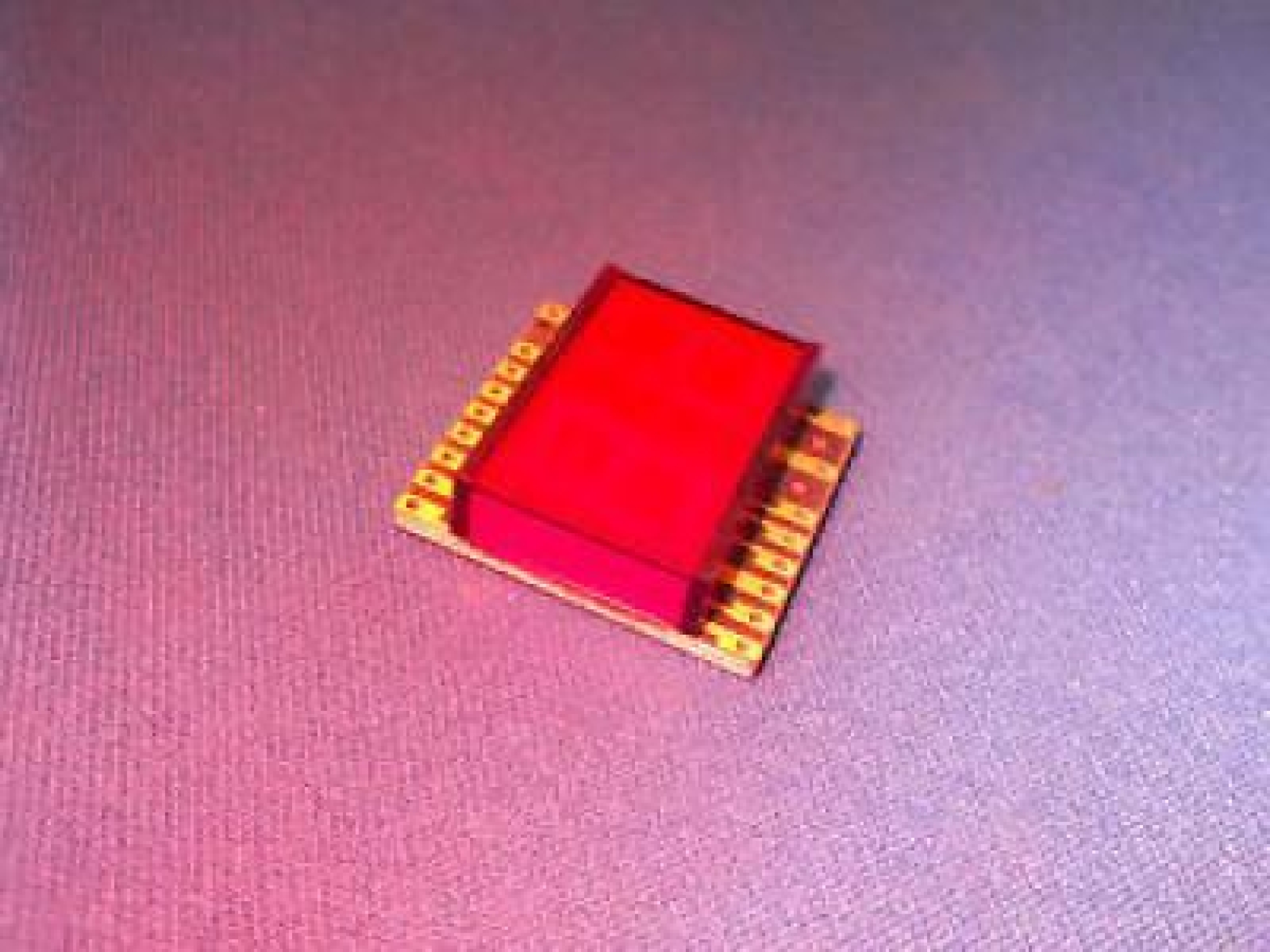

CY7C028V 3.3V 32K/64K x 16/18 Dual-Port Static RAM

Item id: 143 | Vendedor: LeBon (0) 0.0% positivoVer todos os anúncios do vendedor

R$ 100.00

-

Brazil, RS Veranopolis

Brazil, RS Veranopolis -

Compra protegida pelo Programa Shop S-mart

-

Não especificado

-

Devolução: Não aceita devolução

Tenho apenas uma peça. já soldada em adaptador TH.

Architecture

The CY7C027V/028V and CY7037V/038V consist of an array

of 32K and 64K words of 16 and 18 bits each of dual-port RAM

cells, I/O and address lines, and control signals (CE, OE, R/W).

These control pins permit independent access for reads or writes to

any location in memory. To handle simultaneous writes/reads to the

same location, a BUSY pin is provided on each port. Two interrupt

(INT) pins can be utilized for port-to-port communication. Two semaphore

(SEM) control pins are used for allocating shared resources.

With the M/S pin, the devices can function as a master (BUSY pins

are outputs) or as a slave (BUSY pins are inputs). The devices also

have an automatic power-down feature controlled by CE. Each port

is provided with its own output enable control (OE), which allows data

to be read from the device.

Functional Description

The CY7C027V/028V and CY7037V/038V are low-power

CMOS 32K, 64K x 16/18 dual-port static RAMs. Various arbitration

schemes are included on the devices to handle situations

when multiple processors access the same piece of data.

Two ports are provided, permitting independent, asynchronous

access for reads and writes to any location in memory.

The devices can be utilized as stand-alone 16/18-bit dual-port

static RAMs or multiple devices can be combined in order to

function as a 32/36-bit or wider master/slave dual-port static

RAM. An M/S pin is provided for implementing 32/36-bit or

wider memory applications without the need for separate master

and slave devices or additional discrete logic. Application

areas include interprocessor/multiprocessor designs, communications

status buffering, and dual-port video/graphics memory.

Each port has independent control pins: chip enable (CE),

read or write enable (R/W), and output enable (OE). Two flags are

provided on each port (BUSY and INT). BUSY signals that the port is

trying to access the same location currently being accessed by the

other port. The interrupt flag (INT) permits communication between

ports or systems by means of a mail box. The semaphores are used

to pass a flag, or token, from one port to the other to indicate that a

shared resource is in use. The semaphore logic is comprised of eight

shared latches. Only one side can control the latch (semaphore) at

any time. Control of a semaphore indicates that a shared resource is

in use. An automatic power-down feature is controlled independently

on each port by a chip select (CE) pin.

The CY7C027V/028V and CY7037V/038V are available in

100-pin Thin Quad Plastic Flatpacks (TQFP).

Outros anúncios deste mesmo vendedor

PCM54 16-bit DAC

| R$ 80.00 |  |

MMN59120 Opto 7-segment Display CA

| R$ 35.00 |  |

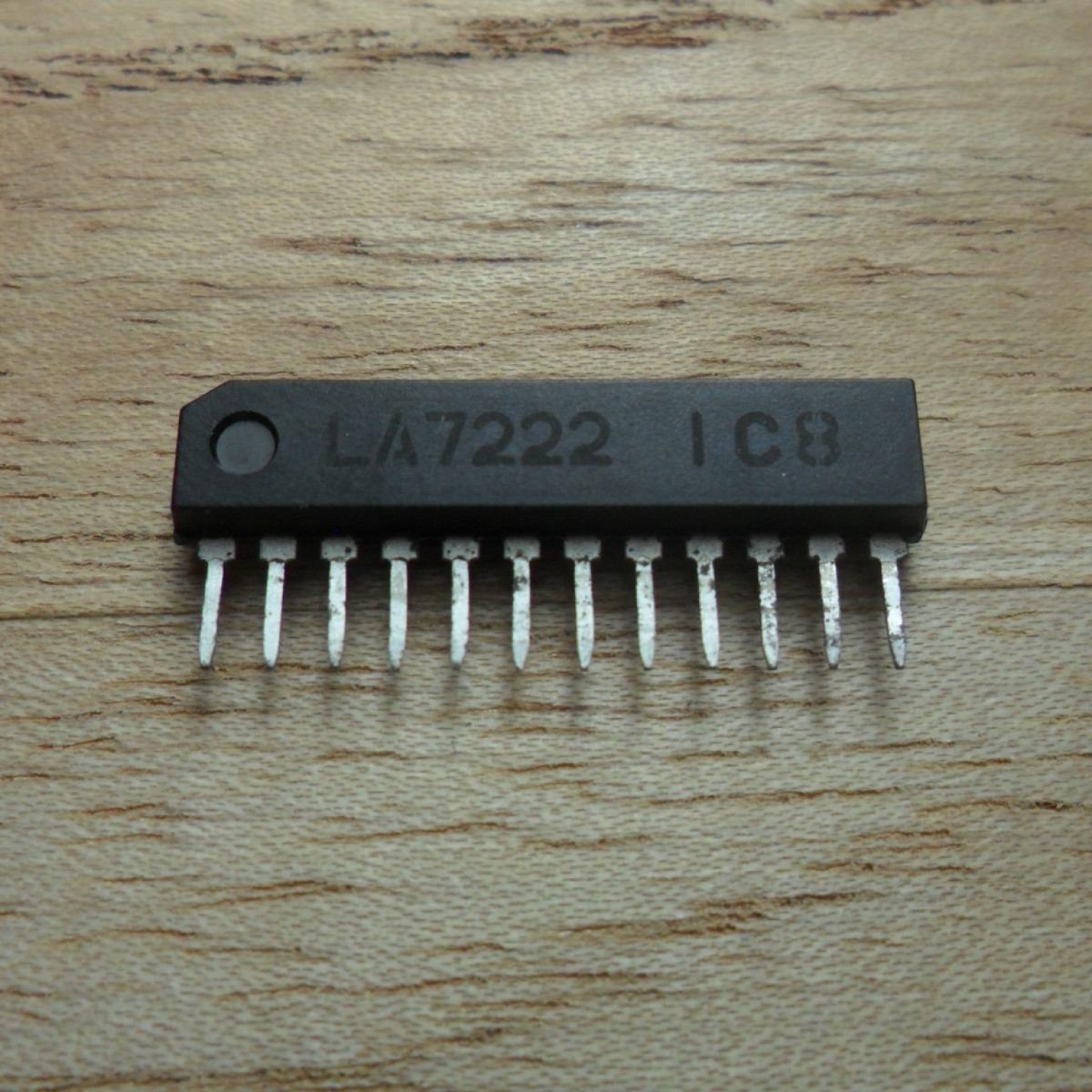

LA7222 Dual SPDT Switch

| R$ 5.00 |  |

Teclado Alesis Quadrasynth Plus Piano 6 Oitavas

| R$ 4,250.00 |  |

Brucutu Ford - Par

| R$ 200.00 |  |

Módulo Servo Do Piloto Automático Ford

| R$ 250.00 |  |

Il Principe - Jogo de Tabuleiro

| R$ 400.00 |  |

IR3109

| R$ 80.00 |  |

Auto Audio - Livro

| R$ 15.00 |  |